ذاكرة الكمبيوتر أشباه الموصلات. الأساسيات الرقمية

ذاكرة الوصول العشوائي (RAM)، أي. ذاكرة الوصول العشوائي المستخدمة المعالج المركزيللتخزين المشترك للبيانات وقابلة للتنفيذ كود البرنامج. وفقا لمبادئ تخزين المعلومات، يمكن تقسيم ذاكرة الوصول العشوائي إلى ثابتة وديناميكية.

يمكن اعتبار ذاكرة الوصول العشوائي (RAM) بمثابة مجموعة من الخلايا، يمكن لكل منها تخزين بتة معلومات واحدة.

في ذاكرة الوصول العشوائي الثابتة، يتم بناء الخلايا عليها خيارات مختلفةمحفزات. بمجرد كتابة جزء من هذه الخلية، يمكنها تخزينها للمدة المرغوبة - كل ما تحتاجه هو الطاقة. ومن هنا اسم الذاكرة - ثابت، أي. البقاء في حالة دون تغيير. تتمثل ميزة الذاكرة الثابتة في سرعتها، ولكن عيوبها هي استهلاك الطاقة العالي وانخفاض كثافة البيانات المحددة، حيث تتكون خلية الزناد الواحدة من عدة ترانزستورات، وبالتالي تشغل مساحة كبيرة على الشريحة. على سبيل المثال، شريحة 4 ميجابت ستتكون من أكثر من 24 مليون ترانزستور، تستهلك الطاقة المقابلة.

في ذاكرة الوصول العشوائي الديناميكية، الخلية الأولية عبارة عن مكثف مصنوع باستخدام تقنية CMOS. مثل هذا المكثف قادر على التخزين لعدة ميلي ثانية الشحنة الكهربائية، والتي يمكن أن يرتبط وجودها ببتة معلومات. عند كتابة منطقية إلى خلية ذاكرة، يتم شحن المكثف، وعند كتابة صفر، يتم تفريغه. عند قراءة البيانات يتم تفريغ المكثف، وإذا كانت شحنته غير صفر، يتم ضبط خرج دائرة القراءة على قيمة واحدة. يتم الجمع بين عملية القراءة (الوصول إلى الخلية) واستعادة (تجديد) الشحنة. إذا لم يتم الوصول إلى الخلية لفترة طويلة، فسيتم تفريغ المكثف بسبب تيارات التسرب ويتم فقدان المعلومات. للتعويض عن تسرب الشحنة، يتم الوصول إلى خلايا الذاكرة بشكل دوري، لأن كل عكس يستعيد الشحنة السابقة للمكثف. إلى المزايا الذاكرة الديناميكيةوتشمل كثافة بيانات عالية واستهلاكًا منخفضًا للطاقة، ومن عيوبها انخفاض الأداء مقارنة بالذاكرة الثابتة.

حاليًا، يتم استخدام الذاكرة الديناميكية (Dynamic RAM - DRAM) كذاكرة وصول عشوائي للكمبيوتر، و ذاكرة ثابتة(Static RAM - SRAM) - لإنشاء ذاكرة تخزين مؤقت عالية السرعة للمعالج.

يتم تنظيم شرائح الذاكرة الديناميكية على النحو التالي: مصفوفة مربعة، ويحدد تقاطع صف وعمود المصفوفة إحدى الخلايا الأولية. عند الوصول إلى خلية معينة، تحتاج إلى تحديد العنوان الخط المطلوبوالعمود. يحدث ضبط عنوان الصف عند تطبيق نبضة قوية خاصة RAS (ومضة العنوان الخام) على مدخلات الدائرة الدقيقة، ويتم ضبط عنوان العمود عند تطبيق نبض CAS (ومضة عنوان العمود). يتم توفير نبضات RAS وCAS بالتتابع واحدة تلو الأخرى عبر ناقل العناوين المتعدد الإرسال.

يحدث التجديد في الدائرة الدقيقة في وقت واحد على طول صف المصفوفة بأكمله عند الوصول إلى أي من خلاياها، أي. يكفي التنقل عبر جميع الخطوط.

(استنادا إلى مواد الإنترنت)

الدوائر التي تستخدم فيها خلية الذاكرة سجل موازي مُسَمًّى ذاكرة الوصول العشوائي الثابتة، لأن يتم تخزين المعلومات فيه طالما أن الطاقة متصلة بالدائرة الدقيقة. مثال على استخدام ذاكرة الوصول العشوائي الثابتة في وحدات التحكم الدقيقة هو ذاكرة البيانات. بالإضافة إلى ذاكرة الوصول العشوائي الثابتة، هناك ديناميكية تستخدم في الدوائر الدقيقة الحديثة ذات الكميات الكبيرة من الذاكرة. على عكس ذاكرة الوصول العشوائي الثابتة، تتطلب ذاكرة الوصول العشوائي الديناميكية تجديدًا دوريًا لمحتوياتها، وإلا سيتم فقدان المعلومات.

هناك عمليتان في ذاكرة الوصول العشوائي: عملية الكتابة وعملية القراءة. لكتابة وقراءة المعلومات، يمكنك استخدام ناقلات البيانات المختلفة (كما هو الحال في معالجات الإشارات)، ولكن في كثير من الأحيان يتم استخدام نفس ناقل البيانات. يتيح لك ذلك حفظ دبابيس الدوائر الدقيقة المتصلة بهذا الناقل وتبديل الإشارات بسهولة بين الأجهزة المختلفة.

يظهر مخطط ذاكرة الوصول العشوائي الثابتة في الشكل. 1. يتم الجمع بين مدخلات ومخرجات الدائرة الدقيقة في هذه الدائرة باستخدام برنامج تشغيل الناقل، والذي يمكنه استقبال البيانات وإخراجها إلى جهاز خارجي. بطبيعة الحال، ستختلف دوائر ذاكرة الوصول العشوائي الحقيقية عن تلك الموضحة في هذا الشكل. ومع ذلك، فإن الرسم البياني أعلاه يسمح لك بفهم كيفية عمل ذاكرة الوصول العشوائي الحقيقية. تظهر صورة ذاكرة الوصول العشوائي (RAM) على مخططات الدوائر في الشكل. 2.

أرز. 1. المخطط الهيكليكبش.

أرز. 2. تمثيل ذاكرة الوصول العشوائي (RAM) على مخططات الدوائر.

تتيح لك إشارة الكتابة WR كتابة المستويات المنطقية الموجودة عند مدخلات المعلومات في خلية ذاكرة الوصول العشوائي الداخلية. تتيح لك إشارة القراءة RD إخراج محتويات خلية الذاكرة الداخلية إلى مخرجات المعلومات الخاصة بالدائرة الدقيقة. في الشكل الموضح. 1 لا يمكن للدائرة إجراء عمليات الكتابة والقراءة في وقت واحد، ولكن هذا ليس ضروريًا في العادة.

يتم تحديد خلية معينة من الدائرة الدقيقة باستخدام الكود الثنائي- عناوين الخلايا. تعتمد سعة ذاكرة الدائرة الدقيقة على عدد الخلايا التي تحتوي عليها، أو ما شابه ذلك، على عدد أسلاك العناوين.

مع كمية كبيرة من الذاكرة، يتم تنفيذه على عدة شرائح. يسمح دبوس تحديد القالب CS بدمج شرائح متعددة لزيادة سعة ذاكرة الوصول العشوائي. يظهر مثل هذا المخطط في الشكل. 3.

أرز. 3. رسم تخطيطي لذاكرة الوصول العشوائي (RAM) المبنية على عدة شرائح ذاكرة.

تتطلب ذاكرة الوصول العشوائي الثابتة مساحة كبيرة للبناء، لذا تكون سعتها صغيرة نسبيًا. يتم استخدام ذاكرة الوصول العشوائي الثابتة لبناء دوائر المتحكم الدقيق نظرًا لسهولة بنائها رسم تخطيطىوالقدرة على العمل بترددات منخفضة بشكل تعسفي وصولاً إلى التيار المباشر. بجانب ذاكرة الوصول العشوائي الثابتةتُستخدم لبناء ذاكرة التخزين المؤقت في أجهزة الكمبيوتر ذات الأغراض العامة نظرًا للأداء العالي لذاكرة الوصول العشوائي الثابتة.

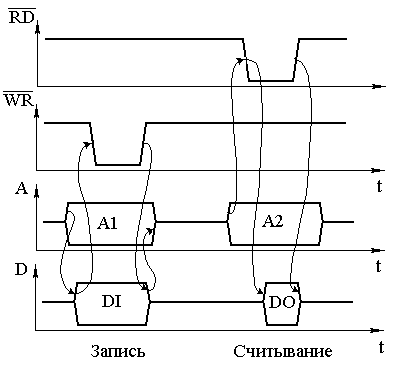

تظهر الرسوم البيانية الزمنية للكتابة والقراءة من ذاكرة الوصول العشوائي الثابتة في الشكل 4.

أرز. 4. مخطط توقيت الوصول إلى ذاكرة الوصول العشوائي (RAM) المعتمد للدوائر المتوافقة مع معيار INTEL.

في التين. 4 أسهم توضح التسلسل الذي يجب أن يتم من خلاله إنشاء إشارات التحكم. في هذا الشكل، RD هي إشارة القراءة؛ WR - إشارة التسجيل؛ أ - إشارات تحديد عنوان الخلية (حيث يمكن للبتات الفردية الموجودة في ناقل العنوان استقبالها معان مختلفة، ثم يتم عرض مسارات الانتقال إلى كل من حالة الوحدة والصفر)؛ DI - معلومات الإدخال المخصصة للكتابة إلى خلية ذاكرة الوصول العشوائي (RAM) الموجودة في العنوان A1؛ DO - قراءة معلومات الإخراج من خلية ذاكرة الوصول العشوائي (RAM) الموجودة في العنوان A2.

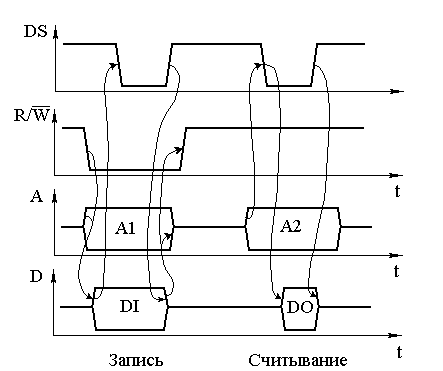

أرز. 5. مخطط توقيت الوصول إلى ذاكرة الوصول العشوائي (RAM) المعتمد للدوائر المتوافقة مع معيار MOTOROLA.

في التين. 5 أسهم توضح التسلسل الذي يجب أن يتم من خلاله إنشاء إشارات التحكم. في هذا الشكل، R/W هي الإشارة لتحديد عملية الكتابة أو القراءة؛ DS - إشارة البيانات القوية؛ أ - إشارات اختيار عنوان الخلية (نظرًا لأن البتات الفردية في ناقل العناوين يمكن أن تأخذ قيمًا مختلفة، يتم عرض مسارات الانتقال إلى الحالتين الواحدة والصفر)؛ DI - معلومات الإدخال المخصصة للكتابة إلى خلية ذاكرة الوصول العشوائي (RAM) الموجودة في العنوان A1؛ DO - قراءة معلومات الإخراج من خلية ذاكرة الوصول العشوائي (RAM) الموجودة في العنوان A2.

أساس خلية الذاكرة في ذاكرة من النوع الثابت هو المشغل. مثل العناصر الأساسيةلتنفيذ الزناد يمكن استخدامها الترانزستورات ثنائية القطب، والميدان. ومع ذلك، لم تجد الأولى تطبيقًا واسعًا نظرًا لارتفاع استهلاك الطاقة لرقائق الذاكرة المبنية عليها. ولذلك، فمن الأمثل للاستخدام تأثير الترانزستور الميدان. في التين. يوضح الشكل 6.1 مشغلًا على ترانزستورات MOS بقناة p مستحثة. لفتح مثل هذا الترانزستور، يجب أن يكون الجهد عند بوابته بالنسبة للمصدر أقل من الصفر: يو زي<0.

أرز. 6.1. رسم تخطيطي لخلية ذاكرة الوصول العشوائي (RAM) من النوع الثابت.

دع الترانزستور في حالته الأولية VT 3 مفتوح و VT 1 مغلق (حالة تخزين صفرية). الترانزستورات VT 2 و VT 4 تعمل كمقاومات وذلك عند استنزاف الترانزستور VT 3 سيكون جهد الإمداد المحتمل + أعلى، وعند استنزاف الترانزستور VT 1- الإمكانيات صفر. الترانزستورات VT 5 و VT 6 تسجيل وقراءة المعلومات. في وضع تخزين البيانات، الجهد على خطوط البت ص 0 و ص 1 يساوي الصفر، والإمكانات على الخط تساوي جهد إمداد الدائرة + أعلى. في هذه الحالة، الجهد مصدر الصرف يو سي في تي 5 على الترانزستور VT 5 يساوي صفر، يو زي.VT 5>0 والترانزستور VT 5 مغلقة. الجهد االكهربى يو زي.VT 6 الترانزستورات VT 6 يساوي صفر وهو مغلق أيضًا.

لتعيين المشغل على حالة واحدة (سجل واحد)، يتم تطبيق احتمال صفر على الخط وعلى خط البت ص 1 احتمال يساوي + أعلى. في هذه الحالة الترانزستور VT 5 سيتم تشغيله بشكل عكسي، أي. يصبح المصدر هو الدبوس المتصل بخط البت ص 1. جهد مصدر البوابة للترانزستور المقلوب VT 5 يصبح أقل من الصفر يو زي.VT 5 <0 и транзистор VT 5 يفتح. تذهب الإشارة الإيجابية إلى بوابة الترانزستور VT 3، بينما يو زي.VT 3 يصبح صفر والترانزستور VT 3 يغلق. ونتيجة لذلك، بوابة الترانزستور VTوصول 1 صفر محتمل. يو زي. VT 1 من هذا الترانزستور يصبح سلبيا والترانزستور VTعند فتح الشكل 1، يتم إنشاء جهد موجب عند استنزافه، وهو ما يتوافق مع الحالة الفردية للمشغل. استنزاف الجهد VT 3 يصبح صفراً

لتسجيل الصفر، من الضروري تطبيق جهد + عند صفر جهد على الخط أعلىإلى خط البت ص 0، بينما من خلال الترانزستور مفتوح VT 6 ـ وصول الجهد الموجب إلى بوابة الترانزستور VT 1 ـ قفله مما يؤدي إلى فتح الترانزستور VT 3. عند استنزاف الترانزستور VT 1، سيتم إنشاء احتمال صفر، وعند استنزاف الترانزستور VT 3 – جهد الإمداد المحتمل .

لقراءة المعلومات المسجلة مسبقًا في المشغل، من الضروري تطبيق الإمكانات الصفرية على الخط فقط. وعلاوة على ذلك، إذا كان الترانزستور مفتوحا VT 1 (حالة واحدة)، ثم الجهد السلبي يو زي.VT 5- الترانزستور مفتوح VT 5ـ ومن خلاله ستدخل الإمكانات العالية إلى خط التفريغ ص 1. إذا كان الزناد في حالة الصفر، فسيتم فتح الترانزستور VT 6 وإمكانات عالية سوف تدخل خط البت ص 0.

في التين. يوضح الشكل 6.2 البنية النموذجية لشريحة ذاكرة الوصول العشوائي الثابتة. يتم تخزين المعلومات في جهاز تخزين. محرك الأقراص عبارة عن مصفوفة مكونة من خلايا الذاكرة التي تمت مناقشتها أعلاه. للبحث عن خلية الذاكرة المطلوبة، يتم تحديد الصف والعمود المطابق لموضع خلية الذاكرة في محرك الأقراص.

يتم استلام عنوان خلية الذاكرة على شكل رقم ثنائي عبر ناقل العناوين في سجل العناوين. يرتبط عدد بتات العنوان بسعة التخزين. تم اختيار عدد صفوف وأعمدة المركم ليكون مساويًا لأس عدد صحيح يساوي اثنين. إذا كان عدد الخطوط صفحة ن=2ن 1 وعدد الأعمدة ن ش=2ن 2، ثم العدد الإجمالي لخلايا الذاكرة (سعة محرك الأقراص) ن=صفحة ن?ن ش=2ن 1+ن 2 =2ن، أين ن=ن 1+ن 2 - عدد بتات العنوان المقبولة في سجل العناوين. على سبيل المثال، مع القدرة ن=2 10 =1024 عدد بتات العنوان ن=10. في هذه الحالة يتم اختياره ن 1=ن 2=5. في هذه الحالة، يكون عدد الصفوف وعدد أعمدة المركم 2 ن 1 =2ن 2 =32. البعد المطلوب لمصفوفة التخزين هو 32×32.

أرز. 6.2. هيكل شريحة ذاكرة الوصول العشوائي (RAM) من النوع الإحصائي.

تنقسم بتات تسجيل العناوين إلى مجموعتين. مجموعة واحدة في ن 1 بت تحدد الرقم الثنائي للخط الذي توجد فيه خلية الذاكرة، والمجموعة الأخرى فيها نرقمان يحددان الرقم الثنائي للعمود الذي توجد فيه خلية الذاكرة. يتم تغذية كل مجموعة من بتات العنوان إلى وحدة فك ترميز الصف أو العمود المقابل. في هذه الحالة، يقوم كل من أجهزة فك التشفير بإنشاء مستوى صفر منطقي على إحدى دوائر الإخراج الخاصة به. يتم تعيين المخرجات المتبقية على مستوى منطقي واحد. يتم تحديد خلية ذاكرة تتأثر بصفرين منطقيين على الأسطر المقابلة في نفس الوقت. وهذا يتوافق مع توفير الصفر المنطقي لخط التشغيل لخلية الذاكرة التي تمت مناقشتها أعلاه.

في وضع القراءة، يتم إخراج محتويات خلية الذاكرة إلى مضخم القراءة ومنه إلى مخرج الدائرة الدقيقة يفعل. في هذه الحالة، يجب أن يكون لإشارة التسجيل مستوى وحدة سلبي. يتم ضبط وضع التسجيل من خلال تطبيق مستوى إشارة صفر نشط على إدخال التسجيل. يفتح مضخم التسجيل وبت المعلومات من مدخل البيانات دي.يدخل خلية الذاكرة المحددة للتخزين، بينما يغلق مضخم القراءة ويتم إخراج البيانات يفعللم يتم تلقي المخططات.

> تحدث العمليات المشار إليها إذا كان مستوى الصفر المنطقي نشطًا عند إدخال اختيار الدائرة الدقيقة. عند المستوى المنطقي عند هذا الإدخال، يتم ضبط جميع مخرجات وحدة فك ترميز الخط على المستوى المنطقي، وتكون الذاكرة في وضع التخزين. يكون تسلسل إمداد إشارات التحكم فرديًا لكل نوع من شرائح الذاكرة. وفي الوقت نفسه، هناك أنماط عامة. دعونا نفكر في تسلسل إمداد إشارات التحكم في أوضاع القراءة والكتابة (الشكل 6.3).

يجب تعيين عنوان خلية الذاكرة النشطة أولاً على ناقل العناوين، في وضعي الكتابة والقراءة. تتم إزالة العنوان من الناقل بعد اكتمال الكتابة إلى الخلية أو القراءة منها. يجب ضبط إحدى إشارات التحكم في تحديد الكتابة أو الشريحة أو كلتيهما على الوضع النشط بعد تعيين العنوان (الفترات الزمنية ر 1 , ر 2 و ر 7 , ر 8) وإزالته حتى تتم إزالة العنوان (فترات زمنية ر 3 , ر 4 و ر 9 , ر 10). وهذا يضمن حالة مقاومة عالية للمحطات الطرفية يفعلو دي.الدوائر الدقيقة، مما يلغي إمكانية التبادل الخاطئ للمعلومات بين شرائح الذاكرة والأجهزة عند تغيير العناوين. في حالة وجود مستوى إشارة سلبي، يتم إيقاف تشغيل مكبر الصوت المؤقت للقراءة أو الكتابة المقابل في كل وضع من أوضاعه. في حالة مستوى الإشارة المنفعلة، يتم إنشاء مستوى إشارة واحد على خط خلية الذاكرة، مما يؤدي إلى فصلها عن الخطوط ص 0 و ص 1 ويخزن المعلومات المسجلة.

في التين. 6.3 يوضح الرسوم البيانية لتوقيت تشغيل ذاكرة الوصول العشوائي (RAM) في حالة تغيير الوضع. أولئك. يتم تنفيذ وضع القراءة بعد وضع الكتابة ووضع الكتابة - بعد وضع القراءة. ولذلك، يتم تعيين كل من الإشارات و. عادة، خلال أوضاع القراءة المتعددة على التوالي وفي غياب الوصول إلى شريحة الذاكرة، يكون للإشارة قيمة ثابتة منطقية. في هذه الحالة، تفعيل الإدخال يفعلنفذت فقط مستوى الصفراشارة ادخال. الأول هو تحديد وضع تشغيل الذاكرة، أي. يتم إعطاء إشارة. إدارة دبوس دي.و يفعليتم تنفيذها بواسطة إشارة تعطى خلال الفاصل الزمني للإشارة.

أرز. 6.3. مخطط توقيت تشغيل ذاكرة الوصول العشوائي (RAM) من النوع الثابت.

قراءة المعلومات من شريحة الذاكرة ممكنة فقط خلال فترة زمنية ر 6 عند اكتمال عملية توليد بيانات المخرجات يفعل(الفاصل الزمني ر 5)، ولم تتم إزالة إشارة اختيار الشريحة بعد. في هذه الحالة، وقت أخذ العينات ر فيتتميز بالفاصل الزمني من لحظة ضبط الإشارة إلى لحظة إنشاء المعلومات عند الإخراج يفعل. في وضع التسجيل، يجب ضبط الإشارة فقط عندما تكون البيانات المراد تسجيلها جاهزة وتصل إلى الإدخال دي.(الفاصل الزمني رأحد عشر). وبالمثل، يجب إعداد البيانات نفسها للتسجيل بحلول الوقت الذي يتم فيه الوصول إلى مستوى الإشارة النشطة (الفاصل الزمني ر 12)، واستمر حتى نهاية هذه الإشارة.

تسمح شرائح ذاكرة الوصول العشوائي (RAM) بزيادة سعة الذاكرة عن طريق زيادة عدد الكلمات المخزنة وزيادة عمق البت لهذه الكلمات. أبسط تنفيذ للأجهزة هو الطريقة الثانية - زيادة قدرة الكلمات المخزنة. لنفكر في بنية الذاكرة التي تبلغ 1 كيلو × 8 بت أو 1024 × 8 بت. الكلمات المخزنة في هذه الذاكرة ستكون ثمانية بت، والعناوين ستكون عشرة بت (1024 = 2 10). ل منظمة مماثلةمن الضروري توصيل ثماني شرائح من ذاكرة الوصول العشوائي (RAM) سعة 1 كيلو؟ 1 بالتوازي مع ناقل العناوين (الشكل 6.4). خط صلب سميك على المخططات الكهربائيةمن المعتاد تصوير الإطارات. يشير الرقم أو الرمز الآخر بجوار سائق الحافلة إلى اسم ذلك السائق الموجود في الحافلة. من الواضح أن كل موصل في الحافلة يجب أن يكون له موصل خاص به اسم فريد. وبالتالي، فإن جميع المحطات التي تحمل نفس الاسم والمتصلة بالحافلة تكون متصلة كهربائيًا.

لجميع الدوائر الدقيقة د 1 – د 8 يتم توفير نفس العنوان. يتم الجمع بين المدخلات والدوائر الدقيقة. تقوم كل شريحة بتخزين بت الكلمة الخاص بها. تتم الكتابة على جميع الرقائق في وقت واحد. وبنفس الطريقة تتم القراءة من جميع الدوائر الدقيقة في نفس الوقت. من الواضح أن تنظيم هذه الذاكرة يسمح لك بتخزين 1024 بايت من المعلومات.

أرز. 6.4. هيكل ذاكرة الوصول العشوائي عند زيادة عمق البت للكلمات المخزنة.

يظهر خيار آخر لتنظيم بنية ذاكرة الوصول العشوائي (RAM) في الشكل. 6.5 والذي يسمح لك بزيادة سعة الذاكرة بنسبة زيادة عدد الكلمات المخزنة. عشر مراتب ثانوية أ 0 – أيتم أيضًا توفير 9 عناوين في البنية قيد النظر لجميع الشرائح الثمانية في وقت واحد د 1 – د 8. في هذه الحالة، جميع المدخلات دي.يتم دمج الدوائر الدقيقة في مدخل واحد مشترك وجميع المخرجات يفعلمجتمعة في مخرج واحد مشترك. ويترتب على ذلك في لحظة معينةالوقت، ينبغي تنشيط واحدة فقط من الدوائر الدقيقة الثمانية. ولهذه الأغراض، يتم استخدام ثلاث بتات عنوان إضافية أ 10 – أ 12، والتي يتم تغذيتها إلى وحدة فك التشفير د 9 اختيار شريحة الذاكرة. من مخرج وحدة فك التشفير، يتم توفير إشارات التنشيط لفصل مدخلات كل شريحة ذاكرة. نظرًا لأن مدخلات الدوائر الدقيقة معكوسة، فيجب أن يكون لجهاز فك التشفير أيضًا مخرجات عكسية ي 0 – ي 7. وبالتالي، يتم تعريف سعة مثل هذا الهيكل على أنها 8 كيلو؟ 1 = 8؟ 1024 بت أو 1024 بايت. السعة الناتجة مشابهة لسعة الهيكل الموضح في الشكل. 6.4، في حين تتطلب معالجتها كمية كبيرةخطوط العنوان في ناقل العناوين. البنية مع زيادة عدد الكلمات المخزنة لها عيبان. يمكن الإشارة إلى الأول على أنه تطبيق أكثر تعقيدًا للأجهزة، والذي يتمثل في إدخال وحدات فك ترميز إضافية. العيب الثاني يرجع إلى انخفاض أداء الذاكرة، حيث يتم تبادل المعلومات عبر زوج واحد من المسامير دي.و يفعلبدلاً من ثمانية أزواج من مخرجات البنية مع زيادة سعة الكلمات المخزنة. ومع ذلك، فإن الهيكل الموضح في الشكل. يتمتع الإصدار 6.5 أيضًا بميزة إمكانية استخدامه في الحالات التي يتجاوز فيها عرض ناقل العنوان عدد مدخلات العنوان للدوائر الدقيقة الفردية.

أرز. 6.5. هيكل ذاكرة الوصول العشوائي عند زيادة عدد الكلمات المخزنة.

من الناحية العملية، غالبًا ما يتم استخدام بنية مدمجة تجمع بين زيادة في عمق البت وعدد الكلمات المخزنة. في هذه الحالة، يتم تشكيل عدد معين من مجموعات مماثلة من الدوائر الدقيقة، مجتمعة في تصميم مع زيادة سعة الكلمات. علاوة على ذلك، يتم دمج هذه المجموعات في بنية واحدة مع زيادة في عدد الكلمات المخزنة. يتم تحديد سعة الكلمة للهيكل المدمج من خلال سعة الكلمة لمجموعة واحدة من الدوائر الدقيقة المتصلة وفقًا لنظام زيادة السعة.

غالبًا ما تتطلب أجهزة الراديو تخزين معلومات مؤقتة، والتي لا تكون قيمتها مهمة عند تشغيل الجهاز. يمكن بناء هذه الذاكرة على الدوائر الدقيقة أو الذاكرة، ولكن لسوء الحظ، هذه الدوائر الدقيقة باهظة الثمن، ولديها عدد صغير من عمليات إعادة الكتابة وسرعة منخفضة للغاية عند القراءة وخاصة كتابة المعلومات. يمكنك استخدامه لتخزين المعلومات المؤقتة. نظرًا لعدم الحاجة إلى الكلمات المحفوظة في نفس الوقت، يمكنك استخدام آلية العنونة المستخدمة في .

تسمى الدوائر التي تستخدم فيها خلية الذاكرة ذاكرة الوصول العشوائي الساكنة - ذاكرة الوصول العشوائي الثابتة(ذاكرة الوصول العشوائي – ذاكرة الوصول العشوائي – ذاكرة الوصول العشوائي) لأن. يتم تخزين المعلومات فيه طالما أن الطاقة متصلة بشريحة ذاكرة الوصول العشوائي (RAM). على عكس ذاكرة الوصول العشوائي الثابتة، تحتاج الدوائر الدقيقة باستمرار إلى تجديد محتوياتها، وإلا سيتم إتلاف المعلومات.

هناك عمليتان في شرائح ذاكرة الوصول العشوائي: عملية الكتابة وعملية القراءة. لكتابة المعلومات وقراءتها، يمكنك استخدام ناقلات بيانات مختلفة (كما هو الحال في معالجات الإشارة)، ولكن في كثير من الأحيان يتم استخدام نفس ناقل البيانات. يتيح لك ذلك حفظ المسامير الخارجية للدوائر الدقيقة المتصلة بهذا الناقل وتبديل الإشارات بسهولة بين الأجهزة المختلفة.

يظهر الشكل 1 الرسم التخطيطي لذاكرة الوصول العشوائي الثابتة. يتم الجمع بين مدخلات ومخرجات ذاكرة الوصول العشوائي في هذه الدائرة باستخدام. بطبيعة الحال، ستختلف دوائر ذاكرة الوصول العشوائي الحقيقية عن تلك الموضحة في هذا الشكل. ومع ذلك، فإن الرسم البياني أعلاه يسمح لك بفهم كيفية عمل ذاكرة الوصول العشوائي الحقيقية. يظهر الرسم الرمزي لذاكرة الوصول العشوائي (RAM) على مخططات الدوائر في الشكل 2.

الشكل 1. مخطط كتلة ذاكرة الوصول العشوائي (RAM)

الشكل 2. التعيين الرسومي لذاكرة الوصول العشوائي (RAM)

تتيح لك إشارة تسجيل WR التسجيل المستويات المنطقية، موجودة عند مدخلات المعلومات إلى خلية ذاكرة الوصول العشوائي الداخلية. تتيح لك إشارة القراءة RD إخراج محتويات خلية الذاكرة الداخلية إلى مخرجات المعلومات الخاصة بالدائرة الدقيقة. في الدائرة الموضحة في الشكل 1، من المستحيل إجراء عملية الكتابة والقراءة في وقت واحد، ولكن هذا ليس ضروريًا في العادة.

يتم تحديد خلية ذاكرة الوصول العشوائي (RAM) معينة باستخدام رمز ثنائي - عنوان الخلية. تعتمد سعة ذاكرة الوصول العشوائي (RAM) على عدد الخلايا التي تحتوي عليها أو، وهو نفس الشيء، على عدد أسلاك العناوين. يمكن تحديد عدد الخلايا في ذاكرة الوصول العشوائي (RAM) من خلال عدد أسلاك العنوان، برفع 2 إلى الطاقة، يساوي المبلغدبابيس العنوان في الدائرة الدقيقة:

يسمح لك دبوس تحديد شريحة CS لشرائح ذاكرة الوصول العشوائي (RAM) بدمج شرائح متعددة لزيادة حجم ذاكرة الوصول العشوائي (RAM). يظهر هذا المخطط في الشكل 3.

الشكل 3. رسم تخطيطي لذاكرة الوصول العشوائي (RAM) المبنية على عدة شرائح ذاكرة

تتطلب ذاكرة الوصول العشوائي الثابتة مساحة كبيرة للبناء، لذا تكون سعتها صغيرة نسبيًا. يتم استخدام ذاكرة الوصول العشوائي الثابتة لبناء دوائر المتحكم الدقيق نظرًا لبساطة إنشاء مخطط الدائرة والقدرة على العمل بترددات منخفضة بشكل تعسفي، وصولاً إلى التيار المباشر. بالإضافة إلى ذلك، يتم استخدام ذاكرة الوصول العشوائي الثابتة لبناء ذاكرة التخزين المؤقت في أجهزة الكمبيوتر ذات الأغراض العامة بسبب الأداء العالي لذاكرة الوصول العشوائي الثابتة.

تتزامن مخططات التوقيت للقراءة من ذاكرة الوصول العشوائي الثابتة مع مخططات التوقيت. تظهر في الشكل 4 مخططات التوقيت للكتابة والقراءة من ذاكرة الوصول العشوائي الثابتة.

الشكل 4. مخطط توقيت الوصول إلى ذاكرة الوصول العشوائي (RAM) المعتمد للدوائر المتوافقة مع معيار INTEL

في الشكل 4، توضح الأسهم التسلسل الذي يجب أن يتم من خلاله إنشاء إشارات التحكم في ذاكرة الوصول العشوائي. في هذا الشكل، RD هي إشارة القراءة؛ WR - إشارة التسجيل؛ أ - إشارات اختيار عنوان الخلية (نظرًا لأن البتات الفردية في ناقل العناوين يمكن أن تأخذ قيمًا مختلفة، يتم عرض مسارات الانتقال إلى الحالتين الواحدة والصفر)؛ DI - معلومات الإدخال المخصصة للكتابة إلى خلية ذاكرة الوصول العشوائي (RAM) الموجودة في العنوان A1؛ DO - قراءة معلومات الإخراج من خلية ذاكرة الوصول العشوائي (RAM) الموجودة في العنوان A2.

الشكل 5. مخطط توقيت الوصول إلى ذاكرة الوصول العشوائي (RAM) المعتمد للدوائر المتوافقة مع معيار MOTOROLA

في الشكل 5، تظهر الأسهم التسلسل الذي يجب أن يتم فيه إنشاء إشارات التحكم. في هذا الشكل، R/W هي الإشارة لتحديد عملية الكتابة أو القراءة؛ DS - إشارة البيانات القوية؛ أ - إشارات اختيار عنوان الخلية (نظرًا لأن البتات الفردية في ناقل العناوين يمكن أن تأخذ قيمًا مختلفة، يتم عرض مسارات الانتقال إلى الحالتين الواحدة والصفر)؛ DI - معلومات الإدخال المخصصة للكتابة إلى خلية ذاكرة الوصول العشوائي (RAM) الموجودة في العنوان A1؛ DO - قراءة معلومات الإخراج من خلية ذاكرة الوصول العشوائي (RAM) الموجودة في العنوان A2.

الأدب:

جنبا إلى جنب مع المقالة "أجهزة ذاكرة الوصول العشوائي الثابتة - ذاكرة الوصول العشوائي (RAM)" اقرأ:

في الكمبيوتر الصغير العادي، ليس من الصعب زيادة سعة الذاكرة؛ كل ما عليك فعله هو تحديد عدد الميغابايت التي تريد إضافتها والمورد الذي يجب الاتصال به. يجب بذل المزيد من الجهد العقلي عند تطوير جهاز به المعالجات الدقيقة التي تسيطر عليهاحيث يكون تخصيص الذاكرة أحد عناصر التصميم، وحيث تتم مشاركة كتل أجهزة التخزين أنواع مختلفة- ذاكرة القراءة فقط (ROM) غير المتطايرة لتخزين البرامج، وذاكرة الوصول العشوائي (RAM) المتطايرة للتخزين المؤقت للبيانات والمكدسات، وكذلك مساحة العملالبرامج.

(انظر الأصل)

أرز. 11.29. معالجات DAC ثنائية القناة 12 بت (مقدمة من Analog Devices)، شريحة - 7537 بعرض تحميل يبلغ 1 بايت؛ ب - شريحة 7547 بعرض تحميل 12 بت.

يتم استخدام ذاكرة القراءة فقط (ROM) غير المتطايرة مع البرامج الثابتة على نطاق واسع في أجهزة المعالجات الدقيقة للتخلص من الحاجة إلى تحميل برنامج في كل مرة يتم فيها تشغيل الجهاز. في هذا القسم سوف ننظر أنواع مختلفةالذاكرة: ثابتة و ذاكرة الوصول العشوائي الديناميكية(ذاكرة الوصول العشوائي)، RPROM (ذاكرة القراءة فقط القابلة لإعادة البرمجة)، ERPZU (ذاكرة القراءة فقط القابلة للمسح كهربائيًا والقابلة لإعادة البرمجة). بمجرد أن تفهمهم قليلاً، لن يكون الاختيار صعبًا. يمكنك الرجوع على الفور إلى الشكل. 11.35، حيث جمعنا أنواع أجهزة التخزين.

ذاكرة الوصول العشوائي الثابتة والديناميكية.

في ذاكرة الوصول العشوائي الثابتة، يتم تخزين البتات في مصفوفات قلابة، بينما في ذاكرة الوصول العشوائي الديناميكية، يتم تخزين البتات في مكثفات مشحونة. ويظل الجزء المكتوب إلى SRAM موجودًا حتى تتم الكتابة فوقه أو يتم إيقاف تشغيل مصدر الطاقة. في ذاكرة الوصول العشوائي الديناميكية، ستختفي البيانات، إن لم يتم "تجديدها"، في أقل من ثانية. بمعنى آخر، ينسى DRAM البيانات باستمرار، ومن أجل تخزينها، يجب عليه بشكل دوري استقصاء "صفوف" مصفوفة البتات ثنائية الأبعاد في شريحة الذاكرة. على سبيل المثال، في ذاكرة الوصول العشوائي بسعة 256 كيلوبت، يجب الوصول إلى كل صف من الصفوف البالغ عددها 256 كل 4 مللي ثانية.قد تتساءل، من قد يفكر في اختيار ذاكرة الوصول العشوائي الديناميكية؟ الحقيقة هي أنه بدون المشغلات، يتم شغل ذاكرة الوصول العشوائي الديناميكية مساحة أقل، مما أدى إلى أن تكون الشريحة ذات السعة الأعلى أرخص. على سبيل المثال، تبلغ تكلفة ذاكرة الوصول العشوائي الثابتة (سعة كيلوبت) الشائعة اليوم حوالي 10 دولارات، أي ضعف السعر الحالي لذاكرة الوصول العشوائي الديناميكية بسعة 1 ميجابت. ونتيجة لذلك، باستخدام ذاكرة الوصول العشوائي الديناميكية، سيكون لديك ذاكرة أكبر 4 مرات بنصف التكلفة.

الآن، ربما تتساءل، من يحتاج إلى ذاكرة الوصول العشوائي الثابتة (هناك شيء يرميك من جانب إلى آخر)؟ الميزة الرئيسية لذاكرة الوصول العشوائي الثابتة هي بساطتها. ليست هناك حاجة لدورات التجديد، ولا داعي للقلق بشأن مزامنتها (تتنافس دورات التجديد مع دورات الوصول إلى الذاكرة العادية وبالتالي يجب أن تكون متزامنة بشكل صارم). في أنظمة بسيطةمع وجود عدد محدود من شرائح الذاكرة، فمن الطبيعي استخدام ذاكرة الوصول العشوائي الثابتة. بالإضافة إلى ذلك، تستخدم معظم ذاكرة الوصول العشوائي الثابتة الحالية تقنية CMOS، وهو أمر ضروري للأجهزة ذات البطارية شحنت. بالمناسبة، تمثل ذاكرة الوصول العشوائي CMOS الثابتة، والتي تتحول تلقائيًا إلى طاقة البطارية عند إيقاف تشغيل الجهاز الرئيسي (باستخدام شريحة إدارة الطاقة من النوع)، ليس بديلا سيئامدمج كما ذاكرة غير متطايرة. ميزة أخرى لذاكرة الوصول العشوائي الثابتة هي أدائها العالي (يتم إنتاج شرائح ذات وقت مميز يبلغ 25 أو أقل)، بالإضافة إلى تخطيط مناسب في أقسام من 8 بت. دعونا نلقي نظرة على كلا النوعين من ذاكرة الوصول العشوائي بمزيد من التفصيل.

ذاكرة الوصول العشوائي الثابتة. لقد واجهنا بالفعل ذاكرة وصول عشوائي ثابتة في تصميم المعالجات الدقيقة لدينا، حيث تم استخدام إحدى هذه السعة من ذاكرة الوصول العشوائي لتخزين البيانات وتكديسها منطقة العمل(تم تسجيل البرنامج في RPOM). يعد تنظيم تبادل البيانات باستخدام ذاكرة الوصول العشوائي الثابتة أمرًا سهلاً مثل تقشير الكمثرى: في دورة القراءة، يمكنك تعيين العنوان واختيار الشريحة (CS) وإشارات تمكين الإخراج (OE)؛ تظهر البيانات المطلوبة على خطوط البيانات القابلة للتعديل بعد الحد الأقصى (وقت الوصول إلى العنوان). في دورة الكتابة، يمكنك إعداد إشارات العنوان والبيانات وCS، ثم (بعد مهلة العنوان) نبض تمكين الكتابة (WE)؛ يتم تسجيل البيانات الصحيحة في نهاية نبضة WE. تظهر حدود التوقيت الحالية لـ 120 ذاكرة وصول عشوائي غير ثابتة في الشكل. 11.30، ومنه يتضح أن "أداء" الذاكرة هو الوقت من تعيين عنوان موثوق إلى بيانات موثوقة (عند القراءة) أو حتى اكتمال دورة الكتابة (عند الكتابة).

أرز. 11.30. 120 ns مزامنة ذاكرة الوصول العشوائي الثابتة. أ- دورة القراءة، ب- دورة الكتابة.

بالنسبة لذاكرة الوصول العشوائي الثابتة، فإن الفاصل الزمني بين عمليات الوصول المتعاقبة للذاكرة ("مدة الدورة") يساوي وقت الوصول؛ بالنسبة لذاكرة الوصول العشوائي الديناميكية، كما سيظهر أدناه، فإن هذا ليس هو الحال.

يمكن أن تتراوح سعة شرائح ذاكرة الوصول العشوائي الثابتة من 1 كيلوبت (أو أقل) إلى 1 ميجابت، بعرض 1 أو 4 أو 8 بت. يتراوح الأداء (وقت الوصول) من 150 إلى 10 أو نحو ذلك. حاليًا، يتم استخدام ذاكرة الوصول العشوائي الثابتة CMOS منخفضة التكلفة على نطاق واسع مع وقت وصول يبلغ 80 نانوثانية، بالإضافة إلى سعة أصغر ولكن ذاكرة الوصول العشوائي CMOS غير الثابتة الأسرع لذاكرة التخزين المؤقت. قد تحتوي خيارات الدوائر الدقيقة على دبابيس منفصلة للمدخلات والمخرجات، ومنفذي وصول، وواحد أو آخر التصميم الخارجي(على سبيل المثال، السكن صف واحد).

قد يكون هذا مهمًا، ولكن لاحظ أنه لا داعي للقلق من أن خطوط بيانات وحدة المعالجة المركزية يجب أن تكون متصلة بنفس منافذ شريحة الذاكرة - ففي النهاية، بغض النظر عن ترتيب الاتصال، عندما تقرأ، ستحصل دائمًا على نفس الشيء الشيء الذي كتبته! هذه الملاحظة صحيحة أيضًا بالنسبة للعناوين. ومع ذلك، لا تحاول القيام بذلك باستخدام ROM.

التمرين 11.18. و لماذا؟

ذاكرة الوصول العشوائي الديناميكية. بالمقارنة مع ذاكرة الوصول العشوائي الثابتة، تعد ذاكرة الوصول العشوائي الديناميكية بمثابة ألم كامل في المؤخرة. في التين. ويبين الشكل 11.31 دورة عادية. يتم تقسيم العنوان (الذي يحتوي، على سبيل المثال، على 20 بت لـ 1 ميجابايت من ذاكرة الوصول العشوائي) إلى مجموعتين ويتم مضاعفة إرساله إلى النصف عدد أصغرالدبابيس، أولاً "عنوان الصف"، مسور بإشارة وميض عنوان الصف - وميض عنوان الصف)، ثم "عنوان العمود"، مسور بإشارة CAS (عنوان العمود - وميض عنوان العمود). تتم كتابة البيانات (أو قراءتها وفقًا لحالة إدخال الاتجاه) بعد إعداد CAS. قبل أن تبدأ دورة الذاكرة التالية، يجب أن يمر بعض وقت "بقاء RAS"، وبالتالي يكون طول الدورة أطول من وقت الوصول؛ على سبيل المثال، قد يكون لذاكرة الوصول العشوائي الديناميكية (DRAM) وقت وصول يبلغ 100 نانوثانية وزمن دورة يبلغ 200 نانوثانية. تبدو دورة التجديد كما هي، لكن بدون إشارة CAS. في الواقع، يعد الوصول العادي إلى الذاكرة أمرًا رائعًا في تجديد الذاكرة، طالما يمكنك التأكد من الوصول إلى جميع عناوين الصفوف المحتملة!

تتوفر ذاكرة الوصول العشوائي الديناميكية، مثل ذاكرة الوصول العشوائي الثابتة، بعرض بيانات يبلغ 1 و4 و8 بت، وبقدرات تتراوح من 64 كيلوبت إلى 4 ميجابت وسرعات تتراوح ما بين 70 إلى 150 نانو ثانية تقريبًا. الأكثر شيوعًا هي شرائح بت الكبيرة، وهو أمر مفهوم: إذا كنت بحاجة إلى مصفوفة ذاكرة كبيرة، مثلاً بحجم 4 ميجا بايت وعرض 16 بت، ولديك ذاكرة وصول عشوائي بسعة 1 ميجابت مع التنظيم، فمن المنطقي استخدام شرائح بت لأن (أ ) سيتم توصيل كل خط بيانات بشريحتين فقط (بدلاً من 16)، مما سيقلل بشكل كبير من الحمل السعوي، و (ب) تشغل هذه الشرائح مساحة أقل لأن عدد دبابيس البيانات الأقل يعوض عن دبابيس العنوان الإضافية.

أرز. 11.31. دورات القراءة والكتابة لذاكرة الوصول العشوائي الديناميكية (Motorola، 120 ns).

بالإضافة إلى ذلك، تعتبر رقائق البتات أرخص بشكل عام. تعتبر الاعتبارات المذكورة أعلاه صالحة إذا كنت تقوم ببناء ذاكرة كبيرة، ولا تنطبق، على سبيل المثال، على المعالج الدقيق البسيط الذي لدينا مع الذاكرة، ومع ذلك، لاحظ أن تقنية تغليف الرقائق عالية الكثافة المحسنة تقلل من أهمية تقليل عدد المسامير.

هناك عدد من الطرق لإنشاء تسلسل العناوين المتعددة الإرسال وRAS وCAS والإشارات المطلوبة للتحكم في ذاكرة الوصول العشوائي الديناميكية. وبما أن ذاكرة الوصول العشوائي هذه متصلة دائمًا بالعمود الفقري للمعالج الدقيق، فإنك تبدأ العمل معها من خلال اكتشاف إشارة (أو ما يعادلها) تشير إلى تثبيتها عنوان صحيحمن مساحة ذاكرة الوصول العشوائي الديناميكية (كما يتضح من سطور العناوين العالية). الطريقة التقليديةيتكون من استخدام مكونات منفصلة بدرجة متوسطة من التكامل لتعدد إرسال العناوين (مضاعفات إدخال القنوات المتعددة) وتوليد إشارات RAS وCAS، بالإضافة إلى إشارات التحكم في مُضاعِف الإرسال.

يتم إنشاء التسلسل المطلوب باستخدام مسجل الإزاحة المسجل على تردد مضاعف تردد الساعةالمعالج الدقيق أو، أفضل، باستخدام خط تأخير استغلالها. لتنظيم دورات التجديد الدورية (RAS فقط)، ستحتاج إلى المزيد من الدوائر المنطقية وعداد يقوم بإحصاء عناوين الصفوف المتسلسلة. كل هذا سيستغرق حوالي 10 مباني.

إحدى الطرق الجذابة، كبديل لدوائر التحكم الديناميكية في ذاكرة الوصول العشوائي "المنفصلة"، هي استخدام PLM، وواحدة أو اثنتين من الدوائر الدقيقة تكفي لتوليد جميع الإشارات اللازمة. ومن الأسهل أن نأخذ على سبيل المثال شريحة خاصة "لدعم ذاكرة الوصول العشوائي الديناميكية". لا يهتم هذا النوع من الدوائر الدقيقة بتعدد إرسال العناوين وتكوين إشارات RAS/CAS فحسب، بل يهتم أيضًا بتحكيم التجديد جنبًا إلى جنب مع تكوين عناوين الصف؛ علاوة على ذلك، فهي تشمل أيضًا برامج تشغيل قويةوالمقاومات snubber، اللازمة لتوصيل صفائف كبيرة من رقائق الذاكرة، كما هو موضح أدناه. عادةً ما تكون وحدات التحكم في ذاكرة الوصول العشوائي الديناميكية هذه مصحوبة بشرائح إضافية للمزامنة، بالإضافة إلى اكتشاف الأخطاء وتصحيحها؛ نتيجة ل مجموعة صغيرةتعمل الرقائق على حل مشكلة دمج ذاكرة الوصول العشوائي الديناميكية في تصميمك تمامًا.

ومع ذلك، تقريبا تماما! تبدأ المشاكل الرئيسية المتعلقة بذاكرة الوصول العشوائي الديناميكية عندما تحاول تحرير نفسك من التداخلات الناتجة عن كل تلك الومضات والقابلة للتوجيه الخطوط الرئيسية. جوهر المشكلة هو أن العشرات من حزم دوائر MOS ينتهي بها الأمر متناثرة على مساحة كبيرة اللوحة الأموحافلات التحكم والعنوان مناسبة لجميع المساكن. لتوصيل عدة عشرات من الدوائر الدقيقة بها، هناك حاجة إلى مراحل إخراج شوتكي قوية؛ ومع ذلك، فإن أطوال الخطوط الطويلة وسعة الإدخال الموزعة، جنبًا إلى جنب مع الحواف الحادة لمراحل الإخراج، تؤدي إلى ظهور "رنين" عالي السعة. يمكنك غالبًا رؤية زيادات سلبية تصل إلى -2 فولت على سطور عنوان ذاكرة الوصول العشوائي! العلاج النموذجي (الذي لا يكون دائمًا ناجحًا تمامًا) هو تضمين مقاومات التخميد المتسلسلة بمقاومة تبلغ حوالي 33 أوم عند خرج كل محرك. مشكلة أخرى هي التيارات العابرة الهائلة، والتي تصل في كثير من الأحيان إلى قيم لكل خط. تخيل دائرة كهربائية صغيرة سائق بت، حيث يتم تبديل معظم النواتج بشكل عشوائي في اتجاه واحد، على سبيل المثال. مستوى عالإلى الأقل. يؤدي هذا إلى تيار عابر يبلغ حوالي 1 أمبير، مما يؤدي لبعض الوقت إلى زيادة إمكانات الطرف المحايد، ومعه جميع المخرجات التي كان ينبغي أن يكون لها مستوى منخفض. المشكلة المذكورة ليست ذات طبيعة أكاديمية بأي حال من الأحوال - لقد لاحظنا ذات مرة فشلًا في تشغيل الذاكرة على وجه التحديد بسبب هذه التيارات العابرة عند الطرف الصفري، والتي تشكلت بسبب زيادة تيارات المحرك. في الوقت نفسه، تبين أن التداخل الذي يمر عبر برامج تشغيل نفس الدائرة الدقيقة كان كافيًا لإكمال دورة الذاكرة!

مصدر إضافي للتداخل في ذاكرة الوصول العشوائي الديناميكية هو التيارات العابرة الكبيرة الناتجة عن الدوائر الدقيقة ككل، وحتى المطورين الأكثر صدقًا يقومون بتضمين معلومات حول هذه الظاهرة في موادهم الفنية (الشكل 11.32). العلاج المعتاد هو تركيب مكثفات تحويلية متصلة بالخط المحايد مع محاثة منخفضة؛ ويعتبر من المعقول تجاوز كل شريحة مكثف السيراميكمع القدرة.

لقد وجدنا أن برامج التشغيل المنطقية ذات المقاومات الخارجية تعمل بشكل جيد مع DRAM، كما تفعل أيضًا برامج تشغيل خاصةالنوع، والذي يتضمن مقاومات snubber متكاملة. يمكن لوحدة التحكم في ذاكرة الوصول العشوائي الديناميكية المذكورة أعلاه، وفقًا للمطورين، خدمة ما يصل إلى 88 شريحة ذاكرة بدون مكونات خارجية، مع إنتاج انبعاثات سلبية لا تزيد عن -0.5 فولت.

أرز. 11.32. التيارات العابرة لذاكرة الوصول العشوائي الديناميكية.

والأهم من اختيار محرك معين هو استخدام خطوط محايدة منخفضة الحث والتحويل المتكرر. الألواح ذات الوجهين ذات الخطوط الأرضية الضيقة ستؤدي حتمًا إلى حدوث مشاكل؛ مجالس التطويرمع لف الأسلاك عادة لا يكون أفضل بكثير.

من المهم أن نفهم أن فشل الذاكرة الناتج عن التداخل يمكن أن يعتمد بشكل كبير على توزيع البتات في البيانات المرسلة ولا يظهر دائمًا في شكل اختبارات بسيطةذاكرة القراءة/الكتابة. أفضل طريقةيمد عملية موثوقةالذاكرة عبارة عن تصميم متحفظ واختبار شامل للذاكرة (مع فحص شكل موجة الذبذبات).

أجهزة تخزين للقراءة فقط (ROM).

تشير ROM إلى ذاكرة غير قابلة للتدمير عند إيقاف تشغيل الطاقة (غير متطايرة)، وتظهر الحاجة إليها في أي مكان تقريبًا نظام الكمبيوتر. على سبيل المثال، في الحواسيب الصغيرة من الضروري أن يكون لديك على الأقل ROM صغير لتخزين سلسلة من الأوامر bootstrap، والذي لا يتضمن فقط تخصيص المكدس وخطوط تهيئة المنفذ والمقاطعة، بل يشمل أيضًا أوامر قراءة نظام التشغيل من القرص. عندما الخاص بك كمبيوتر شخصييقوم بإجراء اختبار للذاكرة ثم يقوم بتحميل DOS، وينفذ أوامر بعض ROM. بالإضافة إلى ذلك، من المعتاد أن يقوم الكمبيوتر الصغير بتخزين جزء من نظام التشغيل في ذاكرة القراءة فقط (عادةً ما تكون الوحدات النمطية الأكثر اعتمادًا على الأجهزة)؛ هذا الجزء يسمى " نظام أساسي"الإدخال/الإخراج" (نظام الإدخال/الإخراج الأساسي، BIOS) ويوفر آلية قياسية لنظام التشغيل للوصول منافذ محددة. تستخدم ROM على نطاق واسع للتخزين طاولات مختلفة، على سبيل المثال، لمولد الأحرف المعروضة على شاشة العرض. وفي الحالة المقيدة، الكل نظام التشغيل، بما في ذلك حتى المترجمين و برامج الرسومات، يمكن أن يكون موجودا في ROM. على سبيل المثال، في كمبيوتر ماكنتوش الصغير، جزء كبير من النظام برمجةمكتوبًا على ROM، ويتم منح المستخدم تقريبًا كل 256 كيلو بايت من ذاكرة الوصول العشوائي. ومع ذلك، نادرًا ما يتم استخدام هذا النهج "المعتمد على ذاكرة القراءة فقط" في الحواسيب الصغيرة نظرًا لعدم مرونته؛ ومع ذلك، لاحظ أنه يمكن إجراء إصلاحات الأخطاء والتحسينات البسيطة للبرامج من خلال التصحيحات المستندة إلى ذاكرة الوصول العشوائي (RAM).في الأجهزة التي تحتوي على تحكم بالمعالجات الدقيقة، يتم استخدام ذاكرة القراءة فقط (ROM) على نطاق أوسع. يقوم ROM بتخزين كافة برنامج مستقلوتستخدم ذاكرة الوصول العشوائي المتطايرة فقط لتخزين المصفوفات والبيانات المؤقتة. وهذا هو بالضبط ما تم القيام به في متوسط الإشارة لدينا. غالبًا ما تكون ذاكرة القراءة فقط مفيدة في الأجهزة الرقمية المنفصلة، على سبيل المثال لبناء أجهزة حالة عشوائية، أو كتخزين جداول التصحيح لخطية وظيفة الاستجابة لنظام القياس. دعونا نلقي نظرة سريعة أنواع مختلفةالذاكرة غير المتطايرة: ROM مع برمجة القناع، بالإضافة إلى EPROM القابل للمسح كهربائيًا.

دورة في الدقيقة. يتم تصنيع ذكريات القراءة فقط القابلة للمسح والبرمجة على شكل شرائح كبيرة ذات نافذة كوارتز. يعد هذا بلا شك النوع الأكثر شيوعًا من الذاكرة غير المتطايرة لأجهزة الكمبيوتر. تستخدم EPROMs تقنية CMOS وMOS وتتكون من صفائف كبيرة من FETs وMOSFET ذات البوابة العائمة التي يمكن شحنها باستخدام عملية "الانهيار الجليدي" لانهيار الطبقة العازلة للبوابة عند تطبيق جهد أكبر من 20 فولت. يتم تخزين البيانات في EPROM إلى أجل غير مسمى على شكل شحنة صغيرة (حوالي 106 إلكترونات) من البوابات "المدفونة" المعزولة، والتي يمكن اعتبارها مكثفات ذات زمن ثابت في حدود القرون. لقراءة حالة مكثف فردي، فإنه يحتاج إلى أن يكون بمثابة بوابة القناة ترانزستور موسفيت. نظرًا لأن الغالق لا يمكن الوصول إليه كهربائيًا، فلا يمكن مسح الشحنة إلا عن طريق تشعيع الدائرة الدقيقة بتيار مكثف من الأشعة فوق البنفسجية لمدة 10-30 دقيقة، مما يتسبب في استنزاف الشحنة المخزنة بسبب ظاهرة الموصلية الضوئية. ونتيجة لذلك، لا يمكن مسح وحدات البايت الفردية من EEPROM بشكل انتقائي.

في الطبعة الأولى من هذا الكتاب، ذكرنا شريحة 2716 "الكلاسيكية"، وهي عبارة عن ذاكرة قراءة فقط تبلغ تكلفتها 25 دولارًا. أما الآن فقد أصبحت كلاسيكية جدًا لدرجة أنه لم يعد بإمكانك الحصول عليها في أي مكان! تتمتع ذاكرة القراءة فقط (ROM) النموذجية في عصرنا بسعة تصل إلى عدة دولارات وسعرها. تتراوح أوقات الوصول عادةً بين 150 و300 نانوثانية، على الرغم من أن شركات مثل Cypress تقدم أقراصًا مدمجة ذات سعة صغيرة وسرعات تصل إلى 25 نانوثانية. لبرمجة EPROM، تحتاج ببساطة إلى تطبيق جهد متزايد عليه (عادةً 12.5 أو 21 فولت)، مع ضبط قيم البايت المطلوبة. تطلبت الخوارزميات الأصلية برمجة كل بايت (مما يعطي 100 ثانية لشريحة 2716، ولكن بالنسبة لذاكرة EEPROM متوسطة الحجم، فإن ذلك يتحول إلى نصف ساعة). يتطلب إصدار ROM الكبيرة من المطورين ابتكار خوارزميات أكثر تقدمًا حيث تتم برمجة كل بايت بسلسلة من النبضات ذات المدة، وبعد كل كتابة تتم محاولة القراءة؛ عندما تتم قراءة البايت بشكل صحيح، يتم إجراء عملية كتابة نهائية تساوي مدتها ثلاثة أضعاف مجموع كافة عمليات الكتابة السابقة. تتم برمجة معظم البايتات مع النبضة الأولى، ونتيجة لذلك، يتم إنفاق حوالي دقيقتين على جميع ذاكرة القراءة فقط.

تعتبر RPOMs ملائمة جدًا للتطوير النماذج الأوليةحيث يمكن إعادة استخدامها بعد المسح. يتم استخدامها أيضًا عند إنتاج مجموعات صغيرة من الأجهزة. الإصدارات الأرخص من EPROMs بدون نافذة كوارتز، تسمى أحيانًا "EPROMs القابلة للبرمجة لمرة واحدة"، متاحة تجاريًا. على الرغم من أن هذه الرقائق لا ينبغي أن تسمى EEPROM، إلا أن المهندسين لا يريدون تغيير الاسم المعتاد. يضمن مصنعو EPROM المحافظون تخزين المعلومات فيها لمدة 10 سنوات فقط. تفترض هذه القيمة الظروف الأسوأ (على وجه الخصوص، درجة حرارة عاليةمما يؤدي إلى تسرب الشحن)؛ في الواقع، لا يبدو أن RPOMs تفقد البيانات إلا إذا حصلت على دفعة معيبة.

إنه نموذجي لـ RPZU رقم محدوددورات إعادة البرمجة، أي المحو وإعادة البرمجة. يتردد المصنعون في إعطاء هذا الرقم، على الرغم من أنه يمكنك افتراض أن الشريحة سوف تتدهور بشكل ملحوظ بعد 100 دورة مسح/برنامج فقط أو نحو ذلك.

أرز. 11.33. متحكم صغير مع EEPROM. أ - متحكم 8 بت مع جهات اتصال لتثبيت ROM؛ ب - متحكم دقيق 8 بت مع ROM مدمج.

ROMs القناع و ROMs المدمجة. تعد ذاكرة القراءة فقط (ROM) القابلة للبرمجة بواسطة القناع فئة من الشرائح المخصصة التي يتم إنشاؤها باستخدام تخطيط البت الذي تحدده. تقوم الشركة المصنعة بتحويل مواصفات البت الخاصة بك إلى قناع معدني، والذي يتم استخدامه بعد ذلك في تصنيع ذاكرة القراءة فقط (ROM). يعد هذا الإجراء مفيدًا للدفعات الكبيرة من الدوائر الدقيقة، ونأمل ألا يخطر ببالك أن تطلب ذاكرة قراءة فقط (ROM) مع برمجة قناع لنموذج أولي. وتتراوح التكاليف النموذجية من 1000 دولار إلى 3000 دولار لكل عملية إنتاج، وتتردد الشركات في قبول طلبات كميات ROM التي تقل عن ألف وحدة. مع مثل هذه الكميات، يمكن أن تكلف الشريحة عدة دولارات.

تحتوي العديد من وحدات التحكم الدقيقة أحادية الشريحة على عدة كيلو بايت من ذاكرة الوصول العشوائي (ROM) وذاكرة الوصول العشوائي (RAM) في نفس الحزمة، بحيث يمكن للجهاز بأكمله الاستغناء عن شرائح الذاكرة الإضافية. في معظم الحالات، تشتمل عائلة المتحكمات الدقيقة على خيارات تتطلب ذاكرة قراءة فقط (ROM) خارجية، وأحيانًا خيارات تحتوي على EPROM مدمج (الشكل 11.33). وهذا يجعل من الممكن، عند تطوير جهاز، استخدام خيار مع RPOM (أو ROM خارجي)، حيث يمكنك كتابة برنامج، وعند إعداد مجموعة من الأجهزة، انتقل إلى وحدات تحكم أرخص مع برمجة القناع.

نوع آخر من ذاكرة القراءة فقط القابلة للبرمجة لمرة واحدة هو ذاكرة القراءة فقط المدمجة. عند تحريرها، يتم تعيين كافة البتات، ولإعادة تعيين البتات المطلوبة، يجب أن يتعرض ROM لها التيار الكهربائي. ومن الأمثلة النموذجية على ذلك شريحة Harris، كما تتوفر أيضًا CMOS PROM (ذاكرة القراءة فقط القابلة للبرمجة) مع حجم وصلة مدمجة على أساس تقنية ثنائية القطب (TTL).

إربزو. يمكن مسح ذاكرة القراءة فقط (ROM) القابلة للبرمجة كهربائيًا بشكل انتقائي وإعادة برمجتها كهربائيًا في نفس الدائرة التي يتم استخدامها فيها كذاكرة. تعتبر هذه الأنواع من ذاكرة القراءة فقط (ROM) مثالية لتخزين ثوابت التكوين ومعلمات المعايرة والمعلومات الأخرى التي لا يمكن كتابتها على ذاكرة القراءة فقط (ROM) قبل تشغيل الكمبيوتر. تستخدم EPROMs، مثل EPROMs، تقنية البوابة العائمة MOS.

مطلوب وحدات ERPZU الأولى زيادة الفولتيةوإجراءات البرمجة الطويلة. الدوائر الدقيقة الحديثةاستخدم جهد إمداد واحدًا وتعمل بشكل أساسي بنفس طريقة SRAM - وبعبارة أخرى، يمكنك إعادة برمجة أي بايت بدورة كتابة واحدة على العمود الفقري. تحتوي شريحة EPROM على دوائر داخلية لتوليد جهد برمجة متزايد، ويلتقط المنطق الداخلي البيانات ويولد تسلسل برمجة يدوم عدة ميلي ثانية، حيث يتم تعيين علامة BUSY طوال مدة العملية أو يتم إنشاء البيانات المقلوبة في دورة القراءة ل تشير إلى أن العملية جاريةالسجلات. تقوم بعض EPROM بتنفيذ كلا البروتوكولين، اللذين يطلق عليهما عادة .

يعد التفاعل مع ذاكرة القراءة فقط أمرًا بسيطًا - ما عليك سوى توصيلها بنفس طريقة ذاكرة الوصول العشوائي العادية واستخدام السطر BUSY لإنشاء المقاطعات (أو قراءة حالة BUSY أو حالة البيانات واستخدامها كعلامة حالة) (انظر الشكل 11.34).

أرز. 11.34. إربزو.

يعد بروتوكول الاستقصاء مناسبًا لأنه يمكن إدخال EPROM في فتحة RAM القياسية دون أي تغييرات في الدائرة (بالطبع، سيتعين على برامجك تضمين خطوط لتحليل البيانات المقروءة والانتظار حتى تتطابق مع ما تكتبه). نظرًا لأن الكتابة إلى EEPROM يتم تنفيذها بشكل نادر نسبيًا، فليست هناك حاجة فعليًا للمقاطعات على سطر RDY/BUSY.

تتوفر EPROMs CMOS في شكل دوائر دقيقة بسعة تبلغ حوالي 10-50 دولارًا أمريكيًا، كما أن وقت الوصول (200-300 ثانية) ووقت البرمجة عند استخدام تحسين الخوارزمية الداخلية) مماثل لتلك الخاصة بـ EPROM القياسي. EPROM، مثل RPZU، يسمح بعدد محدود من دورات القراءة والكتابة. على الرغم من أن الشركات المصنعة تتجنب الاتصال أرقام محددة، يمكنك العثور على إشارة إلى 100000 دورة قراءة وكتابة على .

تعليق. على الرغم من أن EPROMs فريدة من نوعها حيث يمكن إعادة برمجتها مخطط العمل، ويمكن أيضًا برمجتها بشكل منفصل عن مكان الاستخدام، في مبرمج RPOM. وهذا يجعلها ملائمة جدًا لتطوير البرامج المضمنة، حيث لا يتعين عليك الانتظار لمدة نصف ساعة حتى يتم تشغيل EPROM البرنامج القديمالمحمصة تحت الأشعة فوق البنفسجية.

هناك خياران مثيران للاهتمام لـ ERPZU. تنتج الشركات الوطنية وXicor وغيرها شرائح EPROM صغيرة ذات 8 دبابيس. يمكن أن تتراوح سعة هذه الدوائر من إلى بتات؛ إنهم يعملون في الوضع وصول متسلسلوهي مجهزة بإدخال الساعة وخط بيانات واحد. ومن الصعب استخدام هذه الرقائق بدون معالج دقيق؛ ومع ذلك، فهي ملائمة جدًا للتخزين في الأجهزة التي يتم التحكم فيها عن طريق المعالجات الدقيقة كمية صغيرةالإعدادات، الخ. نفس الشركة، Xicor، تنتج "مقياس الجهد القابل للمسح كهربائيًا"، وهو تطبيق مبتكر للذاكرة القابلة للمسح كهربائيًا والتي تخزن موضع "جهة الاتصال الرقمية". تم بناء سلسلة من 99 مقاومًا متساويًا الحجم في هذه الدائرة الدقيقة، ويتم تخزين موضع الصنبور منها، الذي تم ضبطه بواسطة البرنامج، في ذاكرة غير متطايرة متضمنة في نفس الدائرة الدقيقة. ليس من الصعب أن نتصور المشاكل التطبيقية، حيث يكون من المرغوب فيه إجراء معايرة تلقائية أو عن بعد لبعض الأجهزة دون الضبط الميكانيكي لمقابض التحكم.

تم دمج تعديل ظهر مؤخرًا لـ EEPROM يسمى لحظيًا (فلاش). كثافة عالية RPZU مع إعادة البرمجة في دائرة العمل المتأصلة في ERPROM. ومع ذلك، فإن EPROMs الفورية، كقاعدة عامة، لا تسمح لك بمسح البايتات الفردية، كما يمكن القيام به مع EPROMs التقليدية. وبالتالي، فإن EPROM الفوري من Intel يسمح فقط بالمسح الكامل (مثل EPROM)، بينما تسمح شريحة Seeq بمسح قطاع تلو الآخر (512 بايت) أو بالكامل. علاوة على ذلك، فإن معظم EPROMs اللحظية المتوفرة حاليًا تتطلب مصدر طاقة إضافيًا قابلاً للتحويل +12 فولت أثناء المسح/الكتابة، وهو أمر مكلف للغاية عندما تتذكر أن EPROMs التقليدية يتم تشغيلها بواسطة مصدر +5 فولت واحد.

يمكن أن تتحمل EPROMs الفورية من 100 إلى 10000 دورة برنامج.

تستمر تقنية EPROM في التطور، ويسعدنا أن نرى ما ستجلبه لنا بعد ذلك؛ انتظرك ايضا!

ذاكرة الوصول العشوائي غير المتطايرة.

تعتبر RPOMs ملائمة للاستخدام كـ ROM غير متطايرةومع ذلك، غالبًا ما تكون هناك حاجة إلى وجود مادة غير متطايرة كبش. يمكنك استخدام EPROM لهذا الغرض، ولكنها تتميز بدورة كتابة طويلة جدًا (وعدد محدود من دورات القراءة/الكتابة). هناك احتمالان لتحقيق وقت القراءة والكتابة المميز لذاكرة الوصول العشوائي) مع عدد غير محدود من دورات القراءة والكتابة: استخدم إما ذاكرة الوصول العشوائي CMOS الثابتة مع بطارية احتياطية، أو دائرة كهربائية دقيقة Xicor غير عادية تجمع بين ذاكرة الوصول العشوائي الثابتة وEPROM.موضوع البطارية الاحتياطية لذاكرة الوصول العشوائي التي تقتل عصفورين بحجر واحد سبق أن نوقشت: سعر منخفضو السرعه العاليهيتم دمج ذاكرة الوصول العشوائي للقراءة والكتابة مع ذاكرة القراءة فقط (ROM) غير المتطايرة. بالطبع، في هذه الحالة، يجب عليك استخدام ذاكرة الوصول العشوائي CMOS ذات القيمة الحالية الحرجة المعروفة. تنتج بعض الشركات "ذاكرة الوصول العشوائي غير المتطايرة"، وتضعها فيها حالة منتظمةجنبا إلى جنب مع شريحة CMOS ROM بطارية ليثيومو منطقتبديل الطاقة. على سبيل المثال، يمكننا أن نشير إلى الدوائر الدقيقة من شركة Dallas Semiconductor، التي تنتج هذه الشركة أيضًا خطًا من "الموصلات الذكية" التي تحتوي على بطارية ودوائر منطقية، والتي يمكن من خلالها استخدام ذاكرة الوصول العشوائي التقليدية، كما لو كانت في إشارة، العصا السحريةتصبح مستقلة عن الطاقة. يرجى ملاحظة أن ذاكرة الوصول العشوائي غير المتطايرة التي تم تشكيلها بهذه الطريقة ليست خالدة بالمعنى الدقيق للكلمة؛ عمر البطارية، وبالتالي البيانات، حوالي 10 سنوات. كما هو الحال مع ذاكرة الوصول العشوائي الثابتة التقليدية، لا توجد قيود على عدد دورات القراءة والكتابة التي يمكن أن تتحملها الذاكرة. في ذاكرة الوصول العشوائي.

إذا قارنا الخيارين الموصوفين لذاكرة الوصول العشوائي غير المتطايرة، فيبدو أن الخيار المزود ببطارية احتياطية هو الأفضل بشكل عام، لأنه يسمح لك باستخدام أي ذاكرة وصول عشوائي متاحة، طالما أنها تحتوي على وضع إيقاف تشغيل بدون تيار. هذا يعني أنه يمكنك استخدام ذاكرة وصول عشوائي أكبر أحدث القضاياوأيضًا، على سبيل المثال، اختر أسرع ذاكرة وصول عشوائي (RAM)، إذا كان هذا مهمًا بالنسبة لك. على الرغم من أن عمر البطاريات محدود، إلا أنها كافية لمعظم التطبيقات. لتخزين المعلومات على المدى القصير (يوم أو أقل)، يمكنك استبدال بطارية الليثيوم بمكثف مزدوج الطبقة سعة كبيرة; يتم تقديم هذه المكثفات في عبوات صغيرة جدًا بسعة تصل إلى فاراد أو أكثر من قبل شركات باناسونيك وسوهيو وما إلى ذلك.

أجهزة التخزين: ملخص عام.

أرز. 11.35 يلخص أهم الخصائص أنواع مختلفةذاكرة من بين تلك الموضحة في الشكل، نوصي بذاكرة الوصول العشوائي الديناميكية بعرض 1 بت لمصفوفات الذاكرة الكبيرة مع القدرة على القراءة والكتابة، وذاكرة الوصول العشوائي الثابتة بعرض 1 بايت لمصفوفات الذاكرة الصغيرة لأنظمة المعالجات الدقيقة، وEPROM لتخزين البرامج والمعلمات التي لا تتطلب إعادة الكتابة، وإما EPROM (إذا كانت مدة عملية الكتابة لا تهم)، أو ذاكرة الوصول العشوائي الثابتة المدعومة بالبطارية (لتحقيق الاداء العاليالقراءة/الكتابة) للتخزين غير المتطاير للبيانات القابلة للتعديل.

أرز. 11.35. أنواع أجهزة التخزين.